SoC software verification landscape: Where EDA tools fit

May 17, 2016

Blog

Large system-on-chips (SoCs) boasting a few billion gates or more have become a key design challenge for hardware and embedded software verification....

Large system-on-chips (SoCs) boasting a few billion gates or more have become a key design challenge for hardware and embedded software verification. These complex SoC designs integrate an enormous amount of embedded software that requires billions of clock cycles for verification. And it’s leading to a multi-pronged approach to SoC verification that allows moving some aspects of embedded software verification from the post-silicon to the pre-silicon stage.

To set the stage, let’s look at the limitations that traditional verification tools face in serving software-heavy SoC designs. Then, we can see how mixing these tools with virtual techniques can improve the testing of large hardware and software systems before tapeout.

A register-transfer level (RTL) simulator processes a hardware design model. It is highly suitable for hardware debug because it’s relatively easy to use, and quick to set up and compile. However, RTL simulators aren’t suited for embedded software verification where the number of verification cycles required reaches into the billions.

Traditional hardware emulation

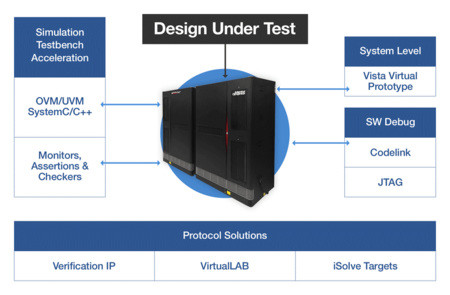

Traditional hardware emulation compiles SoC designs, defined in RTL, onto a hardware platform and runs verification tests on them five to six orders of magnitude faster than simulation. However, though it efficiently debugs hardware and software interactions, emulators have traditionally been configured for in-circuit emulation (ICE) mode where a large number of cables connect the design under test (DUT) to peripherals. It’s carried out through speed adapters that connect the DUT to the real world.

As the number of peripherals grew for complex SoC designs, the virtualization of peripherals drastically increased the use models available for hardware emulation.

FPGA prototyping is predominately used to validate chip designs. Traditionally, software developers use FPGA prototyping for software validation because it’s faster than emulation and allows longer software runs. However, FPGA prototyping involves significant manual intervention that makes debugging software in large SoC designs a tedious and painful task.

The Rise of virtual machines

Enter virtualized prototyping and emulation offering a variety of choices to verify and validate the software in complex SoC designs. Many companies are now starting to use emulation tools to ensure the synergy of software development in their IC designs. For instance, a number of major players in multimedia, mobile and networking markets are using the Mentor Veloce emulation platform to access a mix of virtual and traditional approaches to verification.

For a start, there are virtual prototyping systems that span from a simple stub-code to virtual boards running in QEMU to more advanced virtual prototyping systems to help engineers validate their code. Next, there’s a need for more accurate models that demand virtualization of the interfaces amid the rise in the number of peripherals in modern SoCs.

Here, a hybrid model comprised of emulators and virtual machines can dramatically simplify the SoC verification environment. The hybrid and virtual methodologies are faster than the RTL model running on either simulation or emulation because the processor and some of the surrounding peripherals are modeled at a more abstract level. The more abstract models are easier to create and verify and are more portable.

The Mentor Veloce emulation platform allows debugging of software stacks via tools like Codelink.

The Veloce emulation platform uses virtual prototyping and a virtual lab-like environment to allow SoC designers to perform software debugging via tools such as Codelink and WarpCore. Take WarpCore, for instance, which combines a virtual machine with RTL execution environment, and it comes into play only when there isn’t much hardware involved. More in-depth information is available in the Mentor white paper, Pre-Silicon Software Verification.

Jean-Marie Brunet Marketing Director for the Emulation Division at Mentor Graphics. He has served for over 20 years in application engineering, marketing and management roles in the EDA industry, and has held IC design and design management positions at STMicrolectronics, Cadence, and Micron, among others. Jean-Marie holds a Master’s degree in Electrical Engineering from I.S.E.N Electronic Engineering School in Lille, France.